ISE Design Suite Software Manuals and Help - Xilinx

ISE Design Suite Software Manuals and Help - Xilinx

ISE Design Suite Software Manuals and Help - Xilinx

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

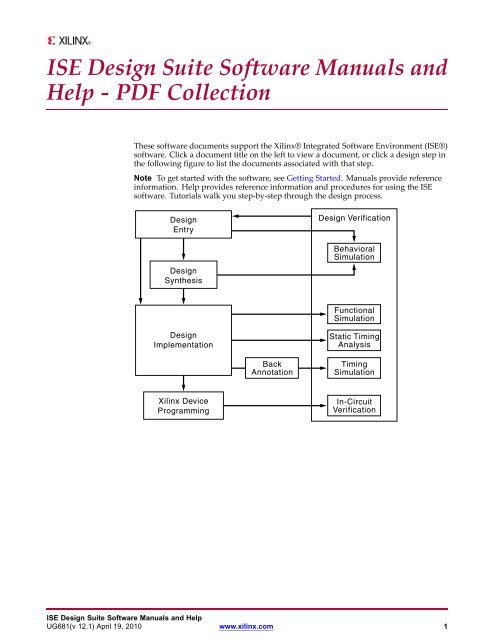

<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong><strong>Help</strong> - PDF CollectionThese software documents support the <strong>Xilinx</strong>® Integrated <strong>Software</strong> Environment (<strong>ISE</strong>®)software. Click a document title on the left to view a document, or click a design step inthe following figure to list the documents associated with that step.Note To get started with the software, see Getting Started. <strong>Manuals</strong> provide referenceinformation. <strong>Help</strong> provides reference information <strong>and</strong> procedures for using the <strong>ISE</strong>software. Tutorials walk you step-by-step through the design process.<strong>Design</strong>Entry<strong>Design</strong>Synthesis<strong>Design</strong> VerificationBehavioralSimulationFunctionalSimulation<strong>Design</strong>ImplementationStatic TimingAnalysisBackAnnotationTimingSimulation<strong>Xilinx</strong> DeviceProgrammingIn-CircuitVerification<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>UG681(v 12.1) April 19, 2010 www.xilinx.com 1

: <strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF CollectionGetting StartedTitleSummary<strong>ISE</strong> <strong>Help</strong> • Provides an overview of the <strong>Xilinx</strong>® Integrated <strong>Software</strong>Environment (<strong>ISE</strong>®), including design flow information<strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: LogicEdition –A Quick Tour(when the Webcast pageappears, click <strong>Design</strong> Tools)EDK SupplementalInformation• Describes how to create, define, <strong>and</strong> compile your FPGAor CPLD design using the suite of <strong>ISE</strong> tools available fromthe Project Navigator• Describes how to migrate past projects to the currentsoftwareProvides a quick tour of the key highlights <strong>and</strong> capabilitiesof the <strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: Logic Edition <strong>and</strong> how it is used intypical design scenarios.• Explains the main steps to getting a design through theentire tool chain: from HDL entry, to place <strong>and</strong> route, <strong>and</strong>all the way through to bitstream generation.• Covers common tasks like assigning pins <strong>and</strong> specifyingconstraints.• Explains the most relevant places to analyze <strong>and</strong> visualizeresults.Note This video replaces the <strong>ISE</strong> QuickStart Tutorial.• Describes how to get started with the EmbeddedDevelopment Kit (EDK)• Includes information on the MicroBlaze <strong>and</strong> thePowerPC® processors• Includes information on core templates <strong>and</strong> <strong>Xilinx</strong> devicedrivers<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>2 www.xilinx.com UG681(v 12.1) April 19, 2010

<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF Collection<strong>Design</strong> EntryTitleSummaryConstraints Guide • Describes each <strong>Xilinx</strong>® constraint, including supportedarchitectures, applicable elements, propagation rules, <strong>and</strong>syntax examples• Describes constraint types <strong>and</strong> constraint entry methods• Provides strategies for using timing constraints• Describes supported third party constraintsConstraints Editor <strong>Help</strong> • Describes how to edit User Constraints Files (UCF) usingthe Constraints Editor, which provides easy access to themost commonly used constraints.• Constraints Editor <strong>Help</strong> is now part of <strong>ISE</strong> <strong>Help</strong>CORE Generator <strong>Help</strong> • CORE Generator provides a catalog of architecturespecific, domain-specific (embedded, connectivity <strong>and</strong>DSP), <strong>and</strong> market specific IP, ranging in complexity fromcommonly used functions, such as memories <strong>and</strong> FIFOs, tosystem-level building blocks, such as filters <strong>and</strong> transforms.Data2MEM User GuideHardware User GuidesNote These manuals areavailable on the xilinx.comwebsite• CORE Generator <strong>Help</strong> explains how to use CORE Generatorto create the exact IP that you need for a project• CORE Generator <strong>Help</strong> explains how to use COREGenerator, <strong>and</strong> is now part of <strong>ISE</strong> <strong>Help</strong>Describes how the Data2MEM tool automates <strong>and</strong> simplifiessetting the contents of BRAM cells on Virtex® devices• Describes the function <strong>and</strong> operation of the latest Virtex®devices <strong>and</strong> Spartan® devices, including information on theRocketIO Multi-Gigabit Transceiver <strong>and</strong> IBM PowerPC®processor• Describes how to achieve maximum density <strong>and</strong>performance using the special features of the Virtex <strong>and</strong>Spartan devices• Includes information on FPGA configuration techniques<strong>and</strong> printed circuit board (PCB) design considerations<strong>ISE</strong> <strong>Help</strong> • Provides an overview of the <strong>Xilinx</strong>® Integrated <strong>Software</strong>Environment (<strong>ISE</strong>®), including design flow information<strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: LogicEdition –A Quick Tour(when the Webcast pageappears, click <strong>Design</strong> Tools)• Describes how to create, define, <strong>and</strong> compile your FPGA orCPLD design using the suite of <strong>ISE</strong> tools available fromthe Project Navigator• Describes how to migrate past projects to the currentsoftwareProvides a quick tour of the key highlights <strong>and</strong> capabilities ofthe <strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: Logic Edition <strong>and</strong> how it is used intypical design scenarios.• Explains the main steps to getting a design through theentire tool chain: from HDL entry, to place <strong>and</strong> route, <strong>and</strong>all the way through to bitstream generation.• Covers common tasks like assigning pins <strong>and</strong> specifyingconstraints.• Explains the most relevant places to analyze <strong>and</strong> visualizeresults.Note This video replaces the <strong>ISE</strong> QuickStart Tutorial.<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>UG681(v 12.1) April 19, 2010 www.xilinx.com 3

: <strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF CollectionTitle<strong>Design</strong> Entry (Cont.)Summary<strong>ISE</strong> Text Editor <strong>Help</strong> • The <strong>ISE</strong> Text Editor lets you create, view, <strong>and</strong> edit text files,such as ASCII, UCF, VHDL, Verilog, <strong>and</strong> TCL files.ISim User Guide• <strong>ISE</strong> Text Editor <strong>Help</strong> is now part of <strong>ISE</strong> <strong>Help</strong>Describes the <strong>ISE</strong> simulator that lets you perform functional <strong>and</strong>timing simulations for VHDL, Verilog <strong>and</strong> mixed VHDL/VerilogdesignsLibraries Guides • Includes <strong>Xilinx</strong>® Unified Library information arrangedalphabetically <strong>and</strong> by functional categoriesPACE <strong>Help</strong>• Describes each <strong>Xilinx</strong> design element, includingarchitectures, usage information, syntax examples, <strong>and</strong>related constraintsDescribes how to use the Pinout <strong>and</strong> Area Constraints Editor(PACE) to define legal pin assignments <strong>and</strong> to create properlysized area constraints for CPLD devices.Note PACE is for use with CPLD devices only. For pinassignment in FPGA Devices, see the PlanAhead User GuidePlanAhead User Guide • Provides detailed information about the PlanAheadsoftwareSchematic <strong>and</strong> SymbolEditors <strong>Help</strong>• Describes the I/O pin planning used in pre-synthesis <strong>and</strong>post-synthesis using the PinAhead environment in ProjectNavigator• Describes a floorplanning methodology for bothpost-synthesis <strong>and</strong> post-implementation that allowsdesigners to constrain critical logic to obtain shorterinterconnect lengths with less delay• For more information on PlanAhead, seehttp://www.xilinx.com/tools/planahead.htm• Describes how to use the Schematic Editor to create a toplevel schematic as input for the Behavioral Simulationor Synthesis steps in the <strong>ISE</strong>® design flow, <strong>and</strong> how tocreate lower-level schematics to instantiate in this top-levelschematic.• Describes how to create a new symbol or edit an existingsymbol to instantiate in a schematic.• Schematic <strong>and</strong> Symbol Editors <strong>Help</strong> is now part of <strong>ISE</strong> <strong>Help</strong>System Generator for DSP • Describes the System Generator DSP developmentenvironments; MATLAB® <strong>and</strong> Simulink®Timing Constraints UserGuide• Describes how to design, simulate, implement <strong>and</strong> debughigh performance FPGA-based DSP systemsDescribes a timing constraint methodology to address timingclosure for high-performance applications<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>4 www.xilinx.com UG681(v 12.1) April 19, 2010

<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF Collection<strong>Design</strong> SynthesisTitle<strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: LogicEdition –A Quick Tour(when the Webcast pageappears, click <strong>Design</strong> Tools)RTL <strong>and</strong> Technology Viewer<strong>Help</strong>Synthesis <strong>and</strong> Simulation<strong>Design</strong> GuideSummaryProvides a quick tour of the key highlights <strong>and</strong> capabilities ofthe <strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: Logic Edition <strong>and</strong> how it is used intypical design scenarios.• Explains the main steps to getting a design through theentire tool chain: from HDL entry, to place <strong>and</strong> route, <strong>and</strong>all the way through to bitstream generation.• Covers common tasks like assigning pins <strong>and</strong> specifyingconstraints.• Explains the most relevant places to analyze <strong>and</strong> visualizeresults.Note This video replaces the <strong>ISE</strong> QuickStart Tutorial.• Describes how to use the RTL Viewer to view a RegisterTransfer Level (RTL) netlist as a schematic after synthesizingwith the XST synthesis tool• Describes how to use the Technology Viewer to view aTechnology Level netlist as a schematic after synthesizingwith the XST synthesis tool• Provides a general overview of designing FieldProgrammable Gate Arrays (FPGA devices) with HardwareDescription Languages (HDLs)• Includes design hints for the novice HDL designer, as wellas for the experienced designer who is designing FPGAdevices for the first timeXST User Guide • Describes <strong>Xilinx</strong> Synthesis Technology (XST) support forHDL languages, <strong>Xilinx</strong> devices, <strong>and</strong> constraintsXST User Guide for Virtex-6<strong>and</strong> Spartan-6 Devices• Describes FPGA <strong>and</strong> CPLD optimization techniques• Describes how to run XST from the Project NavigatorProcess window <strong>and</strong> comm<strong>and</strong> lineThe XST User Guide for Virtex-6 <strong>and</strong> Spartan-6 Devices is botha reference book <strong>and</strong> a guide to methodology. This guide:• Describes the <strong>Xilinx</strong> Synthesis Technology (XST) synthesistool in detail, including instructions for running <strong>and</strong>controlling XST• Discusses coding techniques for designing circuits using aHardware Description Language (HDL)• Gives guidelines to leverage built-in FPGA optimizationtechniques <strong>and</strong> achieve the best implementation on <strong>Xilinx</strong>Virtex®-6 <strong>and</strong> Spartan®-6 devices<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>UG681(v 12.1) April 19, 2010 www.xilinx.com 5

: <strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF Collection<strong>Design</strong> ImplementationTitleComm<strong>and</strong> Line Tools UserGuide (Development SystemReference Guide)Summary• Provides detailed information about converting,implementing, <strong>and</strong> verifying designs with the <strong>Xilinx</strong>®comm<strong>and</strong> line tools• Includes reference information for <strong>Xilinx</strong> FPGA, CPLD,<strong>and</strong> Tcl comm<strong>and</strong> line tools, including syntax, input files,output files, <strong>and</strong> options• Includes SmartXplorer documentation that helps younavigate through the different combinations of MAP <strong>and</strong>PAR options• The Development System Reference Guide has been givena name refresh. Comm<strong>and</strong> Line Tools User Guide bestrepresents the comm<strong>and</strong> line contentFPGA Editor <strong>Help</strong> • Describes how to use the FPGA Editor graphical userinterface to manually place <strong>and</strong> route your FPGA design• Includes information on adding probes to your design <strong>and</strong>working with Integrated Logic Analyzer (ILA) cores <strong>and</strong>cross-probing with Timing AnalyzerXPower Analyzer <strong>Help</strong> • Describes how to use the <strong>ISE</strong> embedded version of theXPower Analyzer software to analyze power consumptionfor <strong>Xilinx</strong> FPGA <strong>and</strong> CPLD devices• XPower Analyzer <strong>Help</strong> is now part of <strong>ISE</strong> <strong>Help</strong><strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>6 www.xilinx.com UG681(v 12.1) April 19, 2010

<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF CollectionBehavioral SimulationTitle<strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: LogicEdition –A Quick Tour(when the Webcast pageappears, click <strong>Design</strong> Tools)ISim User GuideSummaryProvides a quick tour of the key highlights <strong>and</strong> capabilities ofthe <strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: Logic Edition <strong>and</strong> how it is used intypical design scenarios.• Explains the main steps to getting a design through theentire tool chain: from HDL entry, to place <strong>and</strong> route, <strong>and</strong>all the way through to bitstream generation.• Covers common tasks like assigning pins <strong>and</strong> specifyingconstraints.• Explains the most relevant places to analyze <strong>and</strong> visualizeresults.Note This video replaces the <strong>ISE</strong> QuickStart Tutorial.Describes the <strong>ISE</strong> simulator that lets you perform functional <strong>and</strong>timing simulations for VHDL, Verilog <strong>and</strong> mixed VHDL/VerilogdesignsLibraries Guides • Includes <strong>Xilinx</strong>® Unified Library information arrangedalphabetically <strong>and</strong> by functional categoriesSynthesis <strong>and</strong> Simulation<strong>Design</strong> Guide• Describes each <strong>Xilinx</strong> design element, includingarchitectures, usage information, syntax examples, <strong>and</strong>related constraints• Provides a general overview of designing FieldProgrammable Gate Arrays (FPGA devices) with HardwareDescription Languages (HDLs)• Includes design hints for the novice HDL designer, as wellas for the experienced designer who is designing FPGAdevices for the first time<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>UG681(v 12.1) April 19, 2010 www.xilinx.com 7

: <strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF CollectionFunctional SimulationTitle<strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: LogicEdition –A Quick Tour(when the Webcast pageappears, click <strong>Design</strong> Tools)ISim User GuideSummaryProvides a quick tour of the key highlights <strong>and</strong> capabilities ofthe <strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: Logic Edition <strong>and</strong> how it is used intypical design scenarios.• Explains the main steps to getting a design through theentire tool chain: from HDL entry, to place <strong>and</strong> route, <strong>and</strong>all the way through to bitstream generation.• Covers common tasks like assigning pins <strong>and</strong> specifyingconstraints.• Explains the most relevant places to analyze <strong>and</strong> visualizeresults.Note This video replaces the <strong>ISE</strong> QuickStart Tutorial.Describes the <strong>ISE</strong> simulator that lets you perform functional <strong>and</strong>timing simulations for VHDL, Verilog <strong>and</strong> mixed VHDL/VerilogdesignsLibraries Guides • Includes <strong>Xilinx</strong>® Unified Library information arrangedalphabetically <strong>and</strong> by functional categoriesSynthesis <strong>and</strong> Simulation<strong>Design</strong> Guide• Describes each <strong>Xilinx</strong> design element, includingarchitectures, usage information, syntax examples, <strong>and</strong>related constraints• Provides a general overview of designing FieldProgrammable Gate Arrays (FPGA devices) with HardwareDescription Languages (HDLs)• Includes design hints for the novice HDL designer, as wellas for the experienced designer who is designing FPGAdevices for the first time<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>8 www.xilinx.com UG681(v 12.1) April 19, 2010

<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF CollectionStatic Timing AnalysisTitleComm<strong>and</strong> Line Tools UserGuide (Development SystemReference Guide)Timing Analyzer <strong>Help</strong> (forFPGAs)Timing Analyzer <strong>Help</strong> (forCPLDs)Timing Constraints UserGuideSummary• Provides detailed information about converting,implementing, <strong>and</strong> verifying designs with the <strong>Xilinx</strong>®comm<strong>and</strong> line tools• Includes reference information for <strong>Xilinx</strong> FPGA, CPLD,<strong>and</strong> Tcl comm<strong>and</strong> line tools, including syntax, input files,output files, <strong>and</strong> options• Includes SmartXplorer documentation that helps younavigate through the different combinations of MAP <strong>and</strong>PAR options• The Development System Reference Guide has been givena name refresh. Comm<strong>and</strong> Line Tools User Guide bestrepresents the comm<strong>and</strong> line content• Describes how to use the Timing Analyzer software toperform static timing analysis on FPGA designs• Includes information on evaluating <strong>and</strong> generating customtiming analysis reports, cross-probing with synthesis tools,Technology Viewer <strong>and</strong> FPGA Editor• Timing Analyzer <strong>Help</strong> for FPGA devices, is now part of<strong>ISE</strong> <strong>Help</strong>• Describes how to use the Timing Analyzer software toperform static timing analysis on CPLD designs• Includes information on evaluating <strong>and</strong> generating customtiming analysis reportsDescribes a timing constraint methodology to address timingclosure for high-performance applications<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>UG681(v 12.1) April 19, 2010 www.xilinx.com 9

: <strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF CollectionTiming Simulation <strong>and</strong> Back AnnotationTitleComm<strong>and</strong> Line Tools UserGuide (Development SystemReference Guide)<strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: LogicEdition –A Quick Tour(when the Webcast pageappears, click <strong>Design</strong> Tools)ISim User GuideSummary• Provides detailed information about converting,implementing, <strong>and</strong> verifying designs with the <strong>Xilinx</strong>®comm<strong>and</strong> line tools• Includes reference information for <strong>Xilinx</strong> FPGA, CPLD,<strong>and</strong> Tcl comm<strong>and</strong> line tools, including syntax, input files,output files, <strong>and</strong> options• Includes SmartXplorer documentation that helps younavigate through the different combinations of MAP <strong>and</strong>PAR options• The Development System Reference Guide has been givena name refresh. Comm<strong>and</strong> Line Tools User Guide bestrepresents the comm<strong>and</strong> line contentProvides a quick tour of the key highlights <strong>and</strong> capabilities ofthe <strong>ISE</strong>® <strong>Design</strong> <strong>Suite</strong>: Logic Edition <strong>and</strong> how it is used intypical design scenarios.• Explains the main steps to getting a design through theentire tool chain: from HDL entry, to place <strong>and</strong> route, <strong>and</strong>all the way through to bitstream generation.• Covers common tasks like assigning pins <strong>and</strong> specifyingconstraints.• Explains the most relevant places to analyze <strong>and</strong> visualizeresults.Note This video replaces the <strong>ISE</strong> QuickStart Tutorial.Describes the <strong>ISE</strong> simulator that lets you perform functional <strong>and</strong>timing simulations for VHDL, Verilog <strong>and</strong> mixed VHDL/Verilogdesigns<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>10 www.xilinx.com UG681(v 12.1) April 19, 2010

<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF CollectionIn-Circuit VerificationTitleChipScope documentationNote For more informationon ChipScope Pro, includinghow to purchase it, see theChipScope Pro Web pageComm<strong>and</strong> Line Tools UserGuide (Development SystemReference Guide)Summary• Explains how to use the ChipScope Pro Core Generatortool to generate ChipScope Pro cores <strong>and</strong> add them to anFPGA design• Explains how to use the ChipScope Pro Core Inserter tool toinsert cores into a post-synthesis netlist without disturbingthe hardware description language (HDL) source code• Explains how to use the ChipScope Pro Analyzer toolto perform in-circuit verification (also known as on-chipdebugging), including how to view data <strong>and</strong> interactwith ChipScope Pro cores, how to create bitstreams thatare compatible with the ChipScope Pro JTAG downloadfunction, <strong>and</strong> how to download bitstreams to an FPGAusing JTAG• Provides detailed information about converting,implementing, <strong>and</strong> verifying designs with the <strong>Xilinx</strong>®comm<strong>and</strong> line tools• Includes reference information for <strong>Xilinx</strong> FPGA, CPLD,<strong>and</strong> Tcl comm<strong>and</strong> line tools, including syntax, input files,output files, <strong>and</strong> options• Includes SmartXplorer documentation that helps younavigate through the different combinations of MAP <strong>and</strong>PAR options• The Development System Reference Guide has been givena name refresh. Comm<strong>and</strong> Line Tools User Guide bestrepresents the comm<strong>and</strong> line content<strong>ISE</strong> <strong>Help</strong> • Provides an overview of the <strong>Xilinx</strong>® Integrated <strong>Software</strong>Environment (<strong>ISE</strong>®), including design flow information• Describes how to create, define, <strong>and</strong> compile your FPGA orCPLD design using the suite of <strong>ISE</strong> tools available fromthe Project Navigator• Describes how to migrate past projects to the currentsoftware<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>UG681(v 12.1) April 19, 2010 www.xilinx.com 11

: <strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF Collection<strong>Xilinx</strong> Device ProgrammingTitleSummaryData Sheets • Describes the <strong>Xilinx</strong> device familiesHardware User GuidesNote These manuals areavailable on the xilinx.comwebsite• Provides device ordering information• Includes detailed functional descriptions, electrical <strong>and</strong>performance characteristics, <strong>and</strong> pinout <strong>and</strong> packageinformation• Describes the function <strong>and</strong> operation of the latest Virtex®devices <strong>and</strong> Spartan® devices, including information on theRocketIO Multi-Gigabit Transceiver <strong>and</strong> IBM PowerPC®processor• Describes how to achieve maximum density <strong>and</strong>performance using the special features of the Virtex <strong>and</strong>Spartan devices• Includes information on FPGA configuration techniques<strong>and</strong> printed circuit board (PCB) design considerationsiMPACT <strong>Help</strong> • Describes how to use iMPACT to directly configure <strong>Xilinx</strong>FPGAs or program <strong>Xilinx</strong> CPLDs <strong>and</strong> PROMs using a <strong>Xilinx</strong>cable. Explains the procedures for device configuration <strong>and</strong>programming using these modes: Boundary Scan, SlaveSerial, <strong>and</strong> Direct SPI• Describes how to use iMPACT to generate these types ofdevice programming files: System ACE CF, PROM, SVF,STAPL, <strong>and</strong> XSVF• iMPACT <strong>Help</strong> is now part of <strong>ISE</strong> <strong>Help</strong><strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>12 www.xilinx.com UG681(v 12.1) April 19, 2010

<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong> - PDF CollectionLibraries GuidesThe various Libraries Guides contain information about the <strong>Xilinx</strong> Unified Librariesdesign elements, including macros <strong>and</strong> primitives. Each guide targets a specific devicefamily <strong>and</strong> design entry method, <strong>and</strong> covers the following:• <strong>Design</strong> entry methods• Functional categories for design elements• <strong>Design</strong> element informationNote HDL guides also contain instantiation code that you can copy <strong>and</strong> paste intoyour projects.The following Libraries Guides are available:• CPLD Libraries Guide• Spartan®-3 Libraries Guide for HDL <strong>Design</strong>s• Spartan-3 Libraries Guide for Schematic <strong>Design</strong>s• Spartan-3A <strong>and</strong> Spartan-3A DSP Libraries Guide for HDL <strong>Design</strong>s• Spartan-3A <strong>and</strong> Spartan-3A DSP Libraries Guide for Schematic <strong>Design</strong>s• Spartan-3E Libraries Guide for HDL <strong>Design</strong>s• Spartan-3E Libraries Guide for Schematic designs• Spartan-6 Libraries Guide for HDL <strong>Design</strong>s• Spartan-6 Libraries Guide for Schematic <strong>Design</strong>s• Virtex®-4 Libraries Guide for HDL <strong>Design</strong>s• Virtex-4 Libraries Guide for Schematic <strong>Design</strong>s• Virtex-5 Libraries Guide for HDL <strong>Design</strong>s• Virtex-5 Libraries Guide for Schematic <strong>Design</strong>s• Virtex-6 Libraries Guide for HDL <strong>Design</strong>s• Virtex-6 Libraries Guide for Schematic <strong>Design</strong>s<strong>ISE</strong> <strong>Design</strong> <strong>Suite</strong> <strong>Software</strong> <strong>Manuals</strong> <strong>and</strong> <strong>Help</strong>UG681(v 12.1) April 19, 2010 www.xilinx.com 13